11月17日,2018年未来科学大奖颁奖典礼暨F²科学峰会在北京开幕。

在“摩尔定律的终结”研讨会上,斯坦福大学博士,加州大学洛杉矶分校教授兼副主任、CMOS研究实验室负责人Jason C. S. Woo指出,摩尔定律不是物理定律,是具有经济学基础的一个预测。随着摩尔定律的放缓乃至终结,计算机领域正在寻找新的创新路径,基于现有技术从架构创新,算法提升等方式推动计算性能的提升。

以下是演讲内容,enjoy~~

大概始于40年代的时候,工厂里有双极的晶体管,可以说是单晶体管。后来,有一个小组生产出了立体晶体管,推动了整个行业的发展,后来又发展到了IC基础性的行业。

90年代初,有了一些改进,变得更加的集成了,因为可以对十万个晶体管进行部署。现在这种变化还在继续,例如,一开始发明的是点接触晶体管,而今天在英特尔上有近万亿晶体管可以部署。60年的时间,技术改进非常大。

摩尔定律为什么可以这样进行演变?

Moore发现了摩尔定律,他通过简单的观察之后写了一篇论文,发表在电子学期刊上,他提出元器件数量在18—24个月之内会实现翻倍。

但同样重要的是,尽管元器件的数量会不断增加,但组建成本的复杂性,以每年大约两倍的速度增长,这是一个持续的过程,关键在于没有科学的证据,因为这只是一种观察。

因此需要知道它是怎么演变的,为什么最终能够很好的产生这样的效果?工程师怎么创新能一直让摩尔定律发挥作用?

一开始,Moore他去观察的时候,半导体IAC使用的是一些硅,后来发生了很多的变化。原件上数量增加,功率的密度的增加,使得元件管理非常重要,因此这成为了摩尔定律发挥作用的瓶颈。

IBM,在90年代初的时候进行了很多的研究,在那个时候,整个技术是非常复杂和精密的。当时人们都希望创造奇迹,怎么来改变呢?

CMOS,作为一个工程科学家要解决这样的情况,就需要寻找耗电更低的技术,CMOS是非常有趣的特性。因为CMOS非常好的减少它的功率,同时可以减少它的能耗。

1975年的一篇论文提出,如果是在相同的硅面上,可以放更多叠层在底层上,就需要更加关注热量的管理。当然,很多人有其他的考虑,包括兼容性和其他的因素。

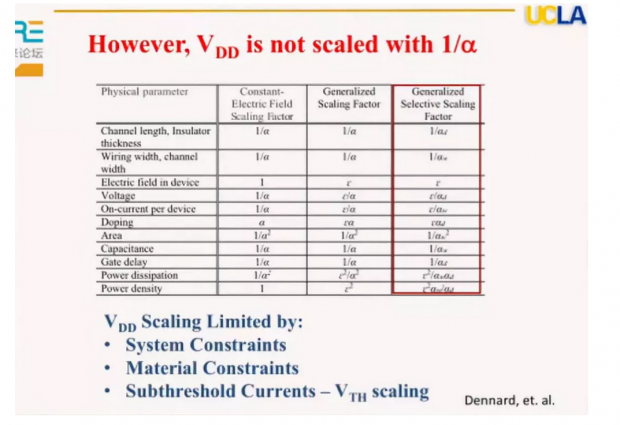

相同的研究组又发表了新的论文,有三种不同的收缩比,这是一开始的收缩比,基本有通用的收缩指数,还有是跟它的功能面成正比的。其中一个非常有意思,就在它的线速,在底层上放了这么多的元件,它的结果是摩尔定律并没有起作用。

当有这么多功能和器件的时候,因为收缩了,所以必须将它进行约束,有不同的约束点,这种约束也是很难做到的,怎么做到这一点?需要发明一种新的方式,将不同的器件联系在一起。如果再看一下IC,2%的晶体管实际是用无线的方式进行联系,后来就成为了最基本的限制。

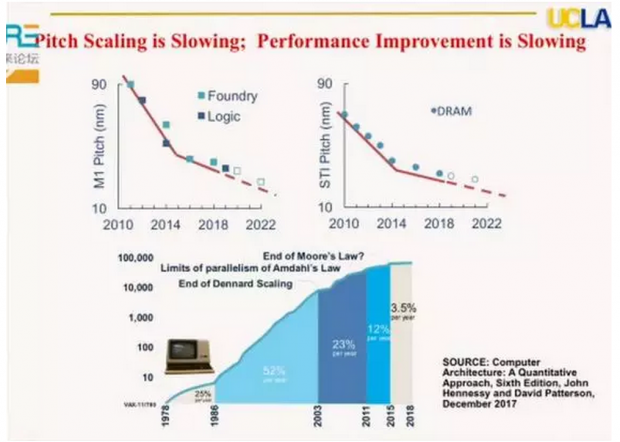

它的规模效应,每两年的缩小0.7倍。一开始是正常的尺寸,基本上是符合这个趋势的,而且是精准的符合这个趋势,一直会持续到2020年。但是到2010年速度就开始放缓了,这是为什么?就是摩尔定律不是定律,是基于经济性或者是因为它的预测性。

当一个公司有效地整合资金和资源的时候,他们就会把它的竞争对手甩在后面,加速尺寸的收缩,例如英特尔。因此在2000年早期的时候,有很多做IC的,但很多人赶不上英特尔的速度。因此,现在只有3个或者4个最主要的技术型公司。

摩尔定律不是物理定律,是具有经济学基础的一个定律。例如在英特尔,CPU一直演进,通过不同的技术节点进行更新,它同时也是符合规律的。也就是说,它的器件的数量成指数级增长,并且会一直持续。到2010年的时候,速度就变慢了,至少功能放大的速度在放缓。

到底什么在推动这些器件数量的增加呢?

在全球,半导体或者消费者行业对于晶体管产品的需求是非常大的,从销售量来看一直是攀升。它是以指数级的数量在增长。行业中的高营收最终受利于公司的研发,同时有更多的资金投入在研发中,这也对应刚才说的摩尔定律是有经济学理论基础的,不仅仅是纯技术或者是纯技术驱动的定律。

2016年,全球半导体的销售达到3350亿美元,在中国都希望自给自足,尽管中国是非常大的电子消费市场,但是这种消费还是由欧洲和美国做主导,在2000做主导的是日本,但是现在日本情况就不一样了。现在,亚太地区主要是由韩国引领的。

毫无疑问,这种器件的数量是根据摩尔定律的预测精准实现,但是还有制造厂建立了集成电路的生产线,而且呈指数级增长。尽管半导体行业赚了很多钱,但是初期的投资额也是相当可观的,因此门槛相当高,不是每个人都有足够的资金投入到半导体行业中,它需要的是一种承诺,也需要很多的决心和决定,才能进入到半导体行业。因为半导体行业的投资总量是极其庞大的。

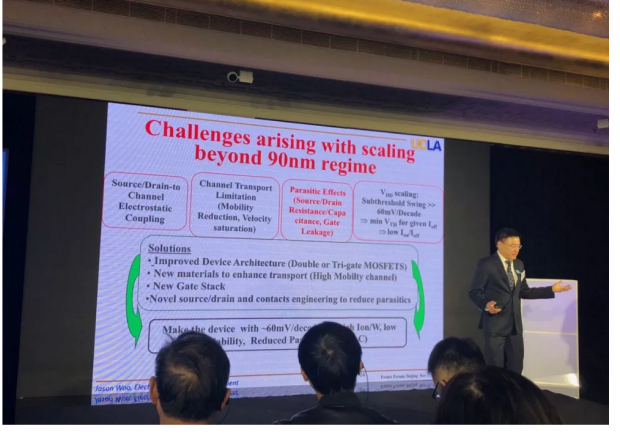

在未来作为科学家或者工程师要探讨的话题是,怎么更加规模化?因为收缩很难做到,有物理空间的限制,越小就越来越难控制。

如何在这么小的表面上去控制这么多的器件,这么多的电线怎么让它的物理尺寸变的更小?一些细小的地方无法进行预测,但是如何让这种细节做的更好?其实难度是很大的,包括器件的性能会限制整个设备的性能。有很多的技术也在不断的演进中,也提出了在过去20年中希望能够去解决刚才所提到的困难,包括更好的创新改进的架构。

由于一些基本的限制,晶体管超过90纳米尺度是不太可能的,这个理论是非常简单的。包括摩尔定律和其他的预测,都是基于历史趋势, 现在的理解完全会忽视一个重要的因素,就是人类的工程和创新的能力,考虑到这一点,有很多物理和化学上的限定,在工程中有这么多创新的领域,一定能帮助找到一种方式,推进整个技术迈向前方,并且符合经济的要求。

在使用不同的原材料的情况下,除了追求尺寸的极限也会寻找其他的极限,包括晶体管设备的速度也在提升,同时也可以根据收缩比进行相同的规模化,所以在实际的速度中要体现出来,因为真正的限制对于的电路来讲,不是提高速度,而是智慧的提供它的使用。

回顾2010年,每一代的CPU总是会有它的速度,除此之外,知道哪怕一个晶体管提供的高速性能IC都不能提供,因为电线是做不到这一点的。基本上来讲,晶体管仅仅是在一个复杂的电路板上有功能。

从设备性能的限制,进入到连接的性能。非常典型的嵌入式的处理器,它的能耗,未来的发展就跟速度一样,大部分的耗能是在电线。

很多的设备也在推动其发展,还有低能耗是要在互联互通的系统中实现。这也是非常重要的一点,为什么技术会通过一些非常复杂的形态来进入和改善? 可以看到,它不是ITW的晶体管,也没办法提供更多的动力。需要非常多的创新,这一般是由英特尔和IBM所带领的。

在下一代的系统架构和超级架构中进行创新,怎么才能具有创新性之举!英特尔不是独一无二的,每个公司都了解这个问题,大家都是公平的,基于实际的模拟仿真。

遵循了同样的情况,整个目标是让晶体管更加高效,负面影响最小。现在要考虑的是非常复杂的晶体管,FinFETs可以产生非常好的电流,希望可以满足新的需求。

英特尔十微米的FinFETs有非常好的连接,电量很高,能够让晶体管密集的组合在一起。这不是最关键的,最关键的在于什么呢?因为这些配置和平台,可以获得非常好的运行能力和效率,从而应对功率方面的缺陷和挑战。在这个基础上进行持续的创新,甚至实现一些指数级的增长。

FinFETs看起来非常的美妙,但是还有很多不尽人意的地方,在很多性能方面还不是非常好。自2000年以来, 就一直在进行尺寸的缩小,在这方面为了能够让功能得到发挥,也在考虑很多方面,像双重收缩,还有一些新的技术,许多新的实际的技术,如果今天看一下的话, 会看到技术带来很多的功能,和以前所拥有的功能是不一样的,现在变得非常的复杂,需要进行很多的计算,需要做出控制,而不是简单的接触。

改进正在减缓,从2015年以来就看到新的改进在放缓,百度、谷歌、因特尔都在进行这方面的研究,但是他们研究的计划和时间表不断的往回缩,进一步发展的速度在放缓。

摩尔定律主要是关于经济学方面的情况;它不可能完全随着性能的变化不断的增加数量,如果要想获得此数据的发展,就应该进行更多的研究方面的投资,在1996年,CPU进行发明之后,大概是每年52%的增长。后来到2010年的时候出现了比例的下降。应该有一个持续的驱动力来推动增长,不光是晶体管,还需要一些新的生态。每个单位的成本也在上升,对高级的节点来说。这个成本的增加非常快。

另一方面,我想谈到的是收缩的问题,在这个问题之外有一个功率的趋势问题。90年代的时候就引起了各方面的注意,如果大家看英特尔芯片的功率密度,就会看到相应的趋势。现在是需要处理热的问题;当然之前也有这样的问题,现在有双晶体管工艺趋势的问题,已经非常棘手了。

低功率的晶体管也非常重要,英特尔预测所有的选项都是开放的,正如他们说的,如果大家还不了解的话,不一定是坏的事情。有一些情况看起来并不好,但是意味着有更多的选项进行研究,需要创新。

除了收缩,还有性能、功率、成本、区域、区分力度、集成都非常重要。未来会有新设备架构启用,从而开发新的功能和新的材料,更加重要的是找到其他的方法来提高密度。

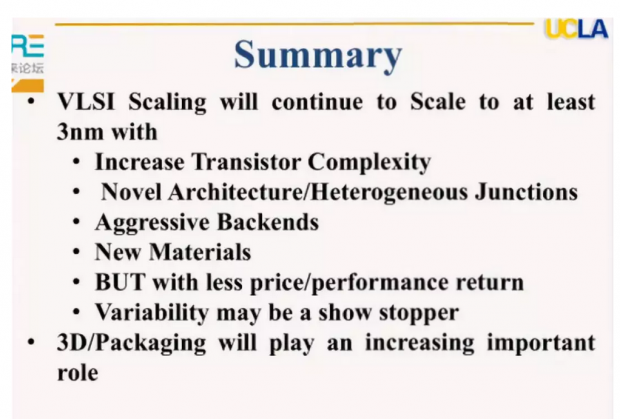

或许会发展到三纳米的程度,其实现在有一些公司已经在行动了,但是如果晶体管复杂性增加,工程师就需要找到新的方法来改进复杂性,甚至改进摩尔定律。从而,找到它真正的本质所在。

0

推荐

京公网安备 11010502034662号

京公网安备 11010502034662号